基板ソリューション プリント基板シミュレーション

高度なシミュレーションで電子回路の安定動作を実現します

USB やHDMI、SATA、PCIe などに代表される通信規格はどんどん高速化しています。

その機能を支える電子回路においては、低電圧駆動高速デバイスが主流になっており、電源ノイズ対策が大きなテーマとなっています。

これらの電子回路の性能を引き出すためには、パターン設計でクリティカルなチューニングが必要です。

実績のあるパターンや層構成、基材を利用しても、デバイスが変われば結果は異なり、また、実績のあるデバイスを利用する場合でも、実装条件が変われば再チューニングが必要になります。

しかし多くの場合、開発工程には余裕がありません。試作のやり直し等を極力避けなければならない場合に、シミュレーション技術が力を発揮します。

特長

-

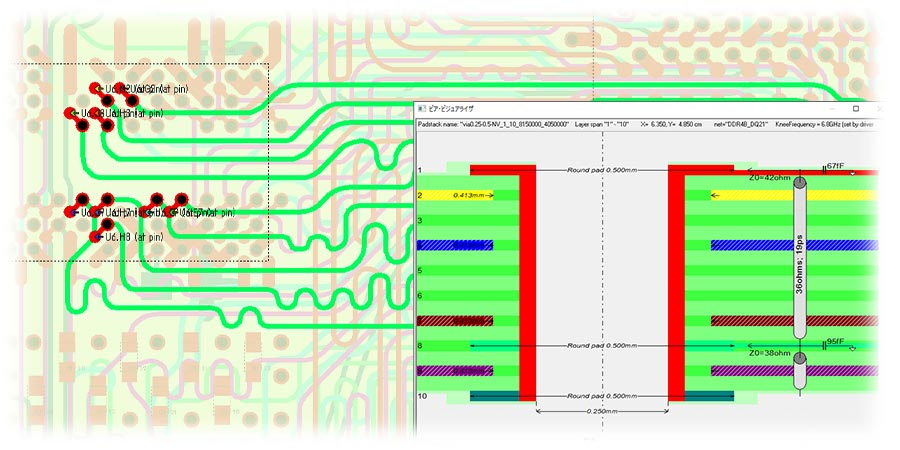

DDR-MEMORY 等の伝送線路のスキューを管理する場合、物理的な配線長を使った計算で管理する場合がありますが、表層と内層とでは伝搬速度が違います。

日本サーキットでは、VIAも考慮した電気長(時間)を用いての検証を行っています。

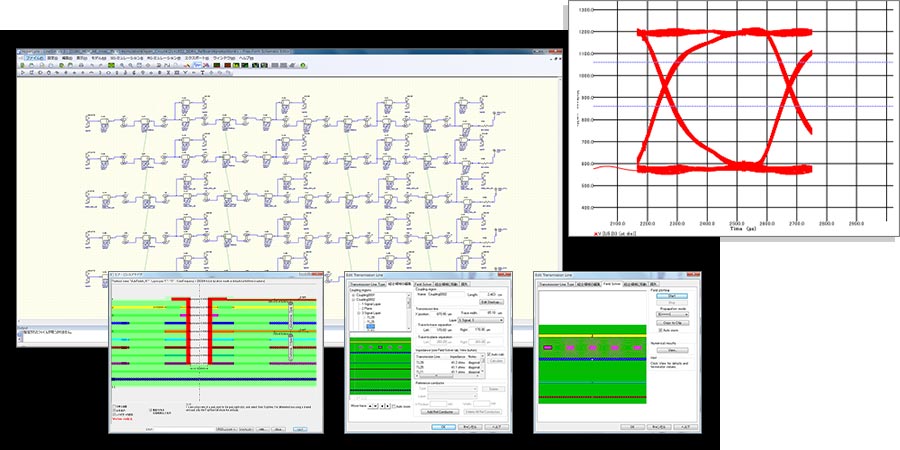

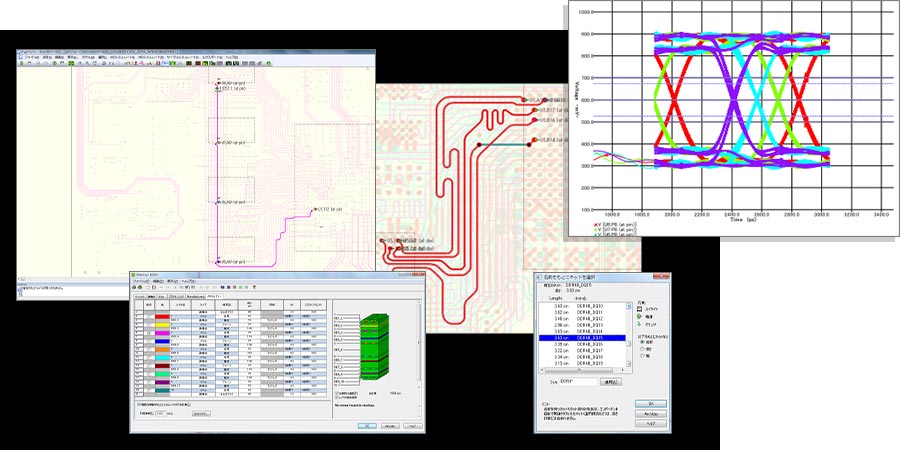

信号品質(SI)シミュレーション

信号波形がLSI 要求のスペック、または通信規格で定められたスペックを満たしており、機器が問題なく動作するかを検証致します。

- プリシミュレーション

- 基板設計初期段階で問題となる可能性のある信号ラインに対し伝送線路解析を行い、最適な部品配置、配線方法(一筆書き配線、等長スター配線、等長T分岐配線など)、終端の処理方法、配線長や伝搬時間の条件の算出をし、基板設計に反映させます。

- ポストシミュレーション

- 配線設計完了後のレイアウトデータをもとに解析を行い、波形診断、配線方法の変更・改善、ダンピングおよび終端抵抗の追加・定数見直し等により問題の解決を行います。

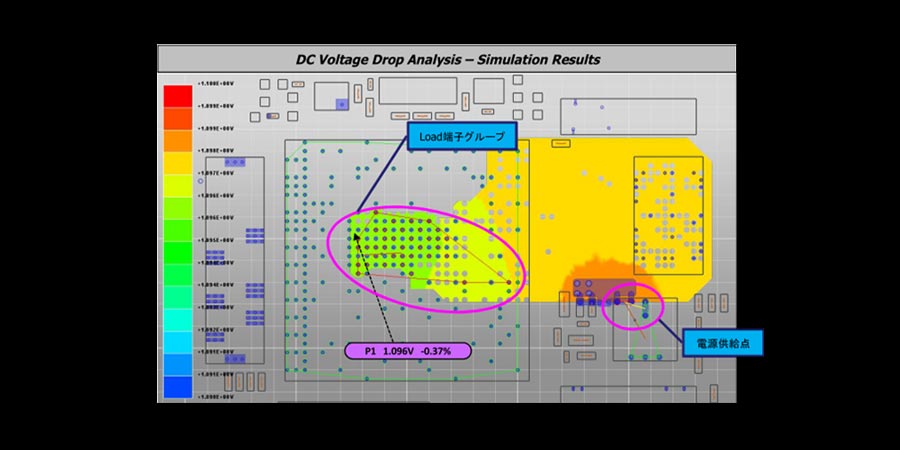

電源品質(PI)シミュレーション

電源電圧がLSI 要求のスペックを満たし、機器が問題なく動作するかを検証致します。この解析を実施することで、電源配線(PDN)、デカップリングキャパシタの個数・定数・配置位置等を電圧降下やインピーダンスの確認で検証します。

- 電源プレーンのIRドロップ解析

-

ANSYS SIwaveを利用してプレーン上にグラデーション表示し、プレーン幅・形状の影響を確認して改善します。

FPGA Core電源端子での電圧がSPEC内であり安全であることが確認できます。

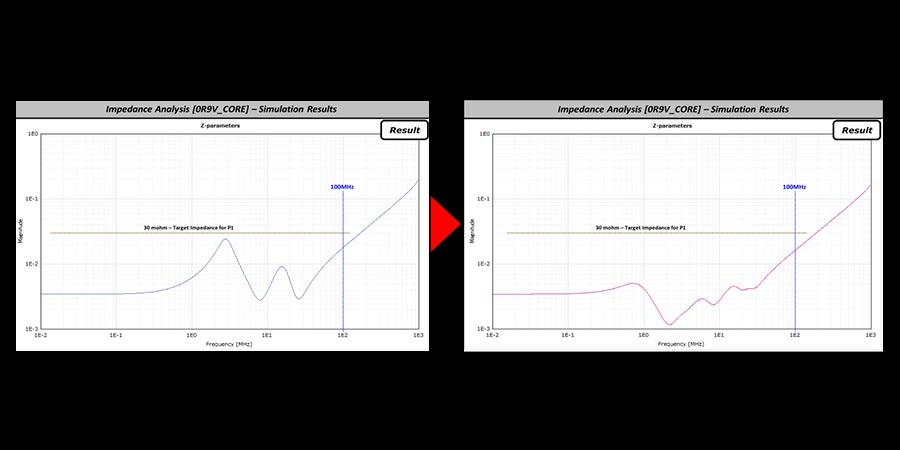

- 電源プレーンのインピーダンス解析

-

【 FPGA Core 電源の改善例 】

デカップリングキャパシタの変更により、200kHz ~20MHz の間が低減されています。

EMC シミュレーション

プリント基板から機器外部へ不要な電磁波を放射しにくい基板になっているか、外部からのノイズの影響で動作不良を発生しやすい基板になっていないかを検証します。

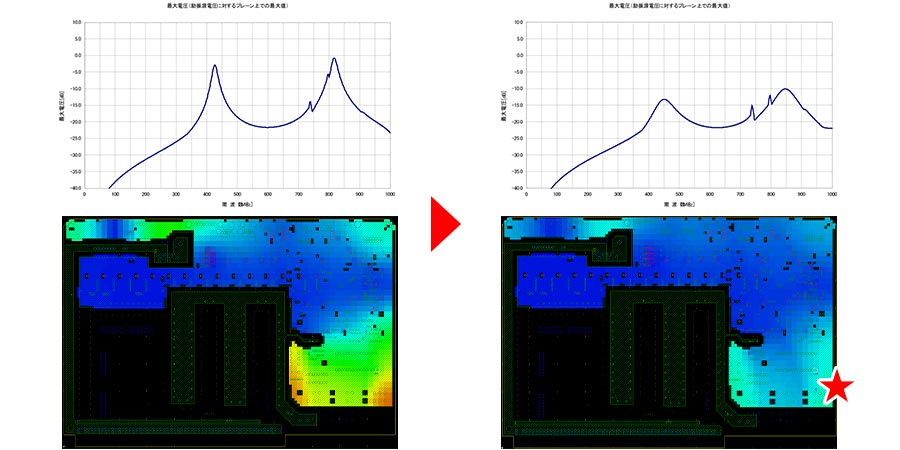

- 電源/GND プレーンの共振解析EMI

- 【スナバ回路追加にて10dB改善できた例 】

共振が起因となるEMI悪化のリスクを回避します。

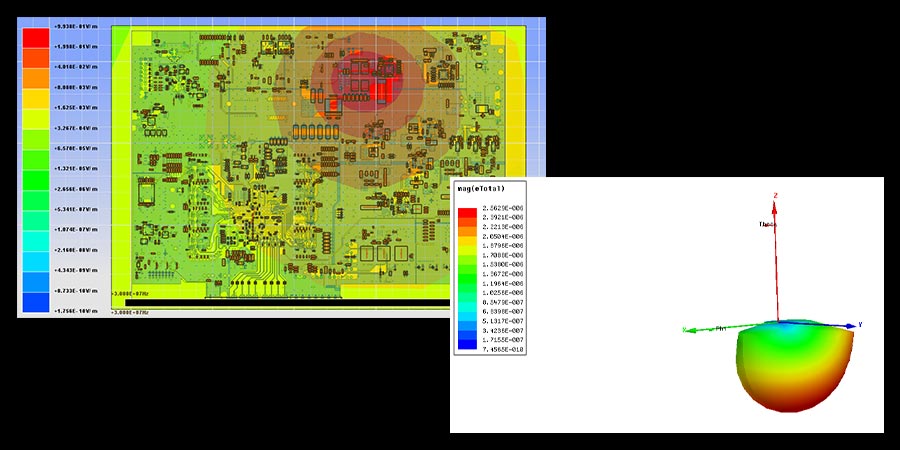

- EMI近傍界、遠方界の解析

- (図左)近傍界ノイズの3D表示/周波数sweepによる動画で確認

- (図右)遠方界ノイズの3D表示

プリント基板シミュレーション実績

- デバイス例

- DDR,DDR2,DDR3,DDR4

- Intel

- Xilinx

- NXP

- Renesas

- Texas Instruments

- Analog Devices

- 各規格

- JEDEC

- PCI Express

- SATA

- USB3.0

- HDMI

- アプリケーション

- オーディオ

- 映像機器

- 通信機器